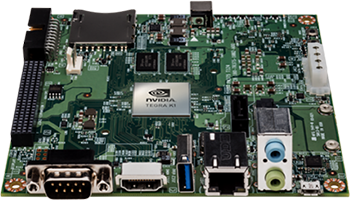

Do naszej oferty dołączył nowy zestaw deweloperski – Jetson TK1 Development Kit. Zestaw Jetson TK1 Development Kit posiada wszystko, czego potrzebuje użytkownik przy zaznajamianiu się z wykorzystaniem mocy obliczeniowej procesorów graficznych – GPU w systemach wbudowanych. Jest zbudowany na bazie rewolucyjnego układu NVIDIA® Tegra® K1 SOC, który wykorzystuje rdzeń NVIDIA Kepler ™ zaprojektowany dla superkomputerów używanych na całym świecie. W pełni funkcjonalna platforma NVIDIA CUDA® pozwala szybko opracować i wdrożyć bardzo wydajny … Czytaj dalej