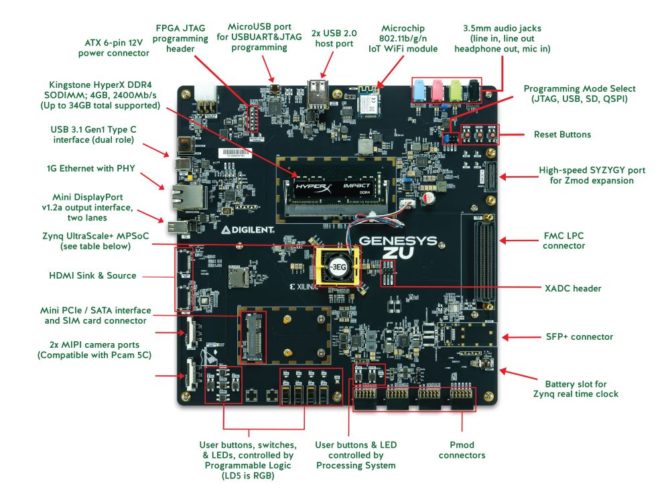

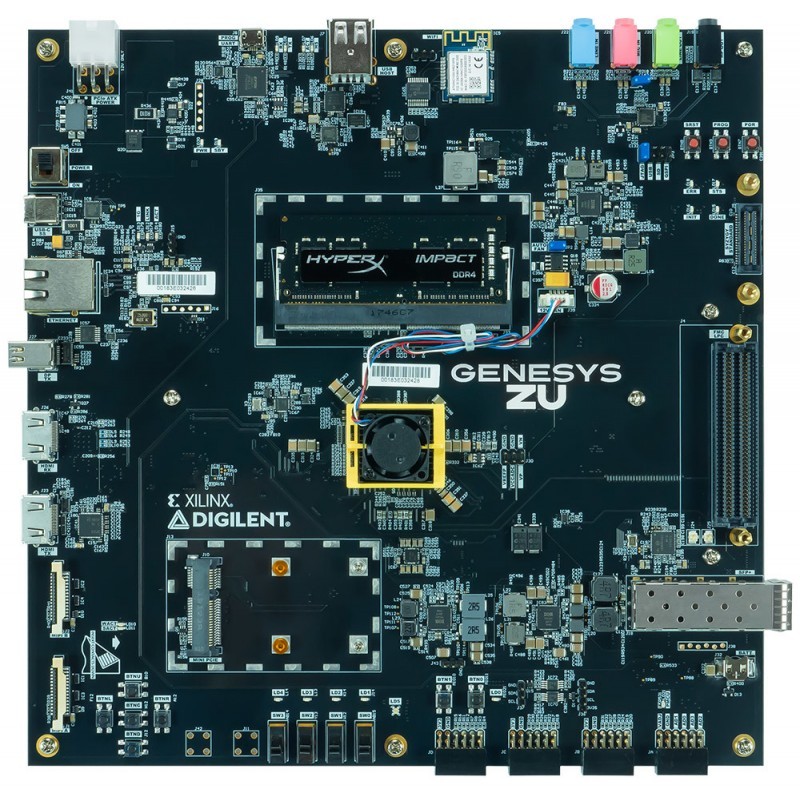

Oferowany przez nas zestaw ewaluacyjny Genesys ZU-5EV z układem Zynq Ultrascale+ MPSoC integruje czterordzeniową platformę ARM Cortex-A53 (1,5 GHz), dwurdzeniowy procesor czasu rzeczywistego Cortex-R5, procesor graficzny Mali-400 MP2 i FPGA. Zestaw ma ulepszony interfejs pamięci, DDR4, USB Type-C 3.1, PCIe, … Czytaj dalej